## ■ SI PI Analysis:

# 광트랜시버 (광대역, PAM-4 변조방식) 구현

- SI PI 분석 설계 최적화 -

Huwin 이 석 이사

brian.lee@huwin.co.kr, 010-5212-1874

**■** 목차

- 1. 설계 개요 (광대역, PAM4 Signaling)

- 2. 분석 툴: ANSYS Electronics Enterprise

- 3. 분석 및 설계 최적화 방법

- <u>3-1. PCB Trace 설계 최적화</u>

- 3-2. Connector-PCB interconnect 설계 최적화

- 3-3. Via interconnect 설계 최적화

- 3-4. AC coupling Capacitor LAND 설계 최적화

- 3-5. PCB 공진 제거

- 3-6. PCB signal return path 문제 해결

- 3-7. PCB Power Ground PI 분석 및 최적화

- 4. Huwin 소개

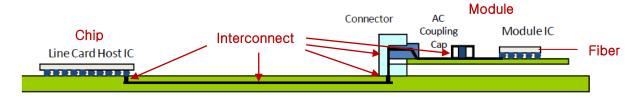

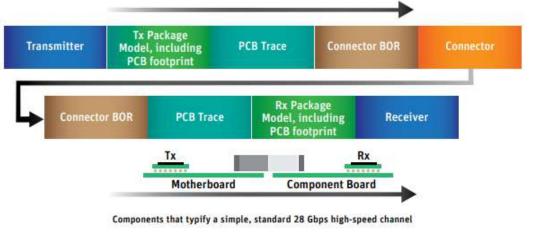

### ■ 1. 설계 개요 : CEI-112G

PCB design guide

### 112Gbps PAM4 Chip to Module interface:

SI 최적화 대상 -> PCB trace, Vias, AC coupling Capacitor, Connector, copper Cable

- => Electrical spec. : Ch. Loss, Impedance, Eye Height/Width

- => 3D EM 분석을 통해 Electrical Spec. 을 만족하도록 최적화 설계 및 검증이 필수임

- => Cost effective 설계 구현을 위해 적절한 재질 선정 및 interconnection 설계가 매우 중요함

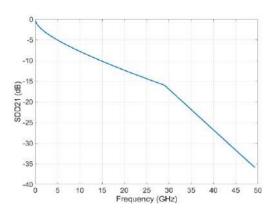

Ch. Loss (SDD21 of end-to-end limit):

\* ~80GHz 3D EM 분석 통한 Loss, Impedance 최적화 설계 필요함.

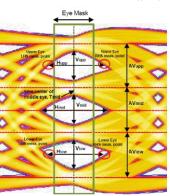

#### PAM4 signal Eye Parameters:

\* PAM4의 경우 NRZ 대비 noise margin 이 30%이상 감소하므로, crosstalk, reflections, power noise 를 최소화 하도록 설계하여야 함.

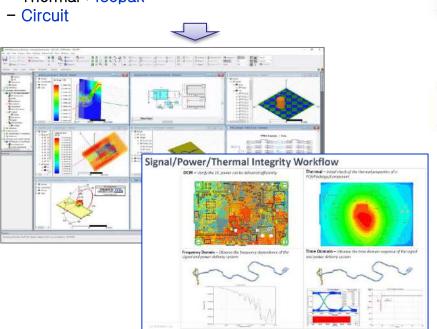

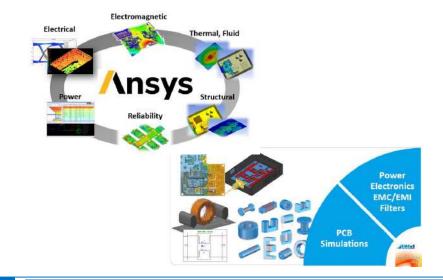

### ■ 2. 분석 툴: ANSYS Electronics Enterprise

### 3D EM 모델링/분석 및 PCB SI/PI:

#### **ANSYS Electronics Enterprise:**

=> Electronics 분석 위한 통합 UI 및 Solvers 패키지

- 3D EM: HFSS(High Freq.), Maxwell(Low Freq.)

- PCB EM SI/PI: Slwave

- RLC Extraction: Q3D Extractor

- Thermal : Icepak

Source: "Deep Channel Analysis for High-Speed Interconnect Solutions", Ansys Advantage 2 017

## ■ <u>3. 분석 및 설계 최</u>적화 방법 :

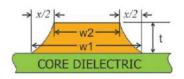

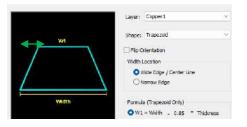

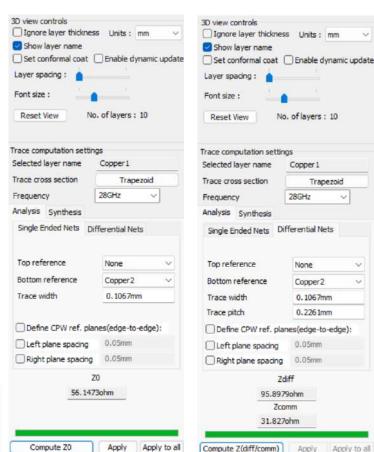

#### 3-1. PCB Trace 설계 최적화:

- PCB EM SI/PI: Slwave 이용 PCB Trace Impedance 확인 및 width/ space 최적화

$$Etchback(x) = w1 - w2$$

$$Etch\,Factor\,(F) = \frac{w1 - w2}{t}$$

\* Etch Factor 적용시 PCB trace 의 Impedance 가 ~5옴 정도 영향을 받으므로 PCB 공정의 parameter 를 적용하여 PCB trace 의 impedance 를 확인 및 설계 시 trace width 와 space 의 최적 값을 적용함.

#### PCB Trace design issues

\* PCB trace 의 공정 편차 고려하여 정확한 Impedance 설계로 튜닝

a. b. c 설계 변수 -> Slwave 이용 Trace 분석 후 정확한 Z0 값 튜닝 필요

Single ended Z0

Differential Z0

Zdiff

95.8979ohm Zcomm 31.827ohm

No. of layers: 10

Copper 1

28GHz

Differential Nets

None

Copper2

0.1067mm

0.2261mm

0.05mm

Apply

Apply to all

Trapezoid

### ■ 3. 분석 및 설계 최적화 방법 :

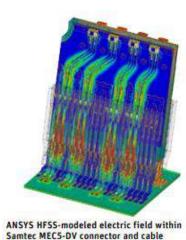

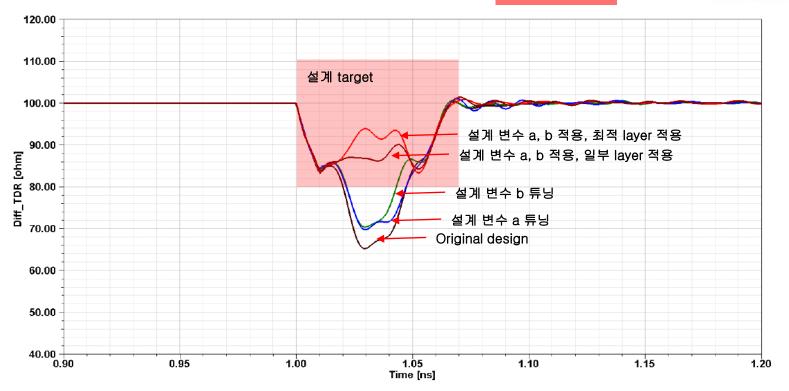

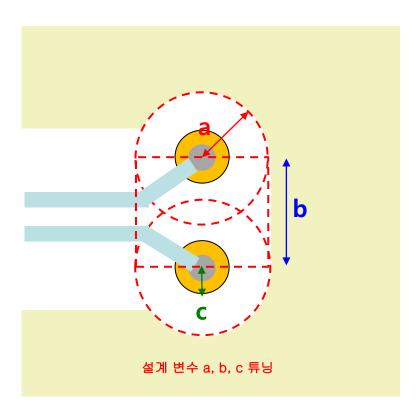

#### 3-2. Connector-PCB interconnect 설계 최적화:

- 3D EM: HFSS(High Freq.) 이용 Connector pad 부분 TDR impedance 최적화

#### Connector – PCB interconnect design issues

\* Pad contact 에 의한 stub, pad 부분 impedance, Ground reference plane 의 void 설계 등 최적화 필요함.

a, b, c 설계 변수 -> 0.1mm 단위로 3D EM 분석 후 TDR 확인하여 최적화 튜닝 필요

## ■ 3. 분석 및 설계 최적화 방법 :

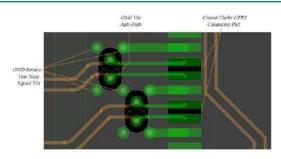

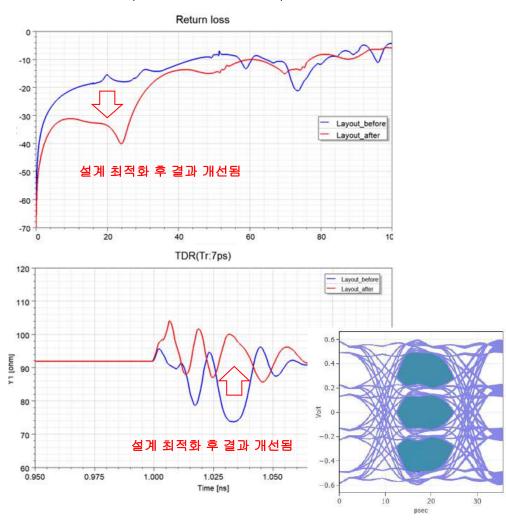

### 3-3. Via interconnect 설계 최적화:

- 3D EM : HFSS(High Freq.) 이용 Via 부분 TDR impedance 최적화

#### PCB via design issues

\* via size 및 anti pad 설계에 의한 TDR Impedance 튜닝 필요함.

## ■ 3. 분석 및 설계 최적화 방법 :

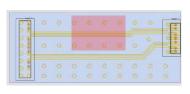

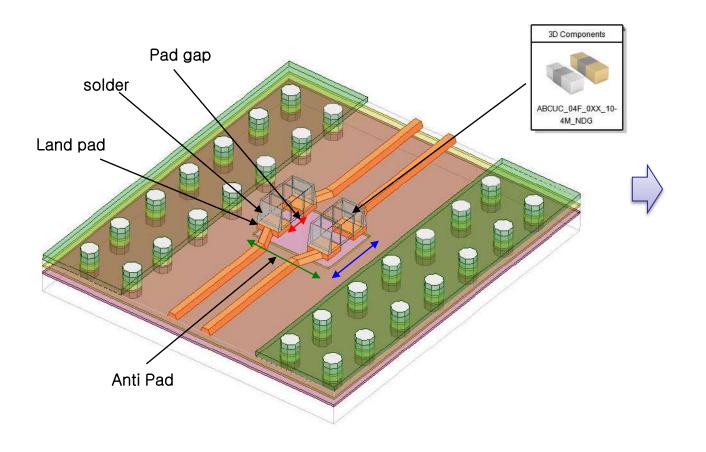

### 3-4. AC coupling Capacitor LAND 설계 최적화:

- 3D EM: HFSS(High Freq.) 이용 AC coupling Capacitor layout 부분 TDR impedance 최적화

## ■ 3. 분석 및 설계 최적화 방법 :

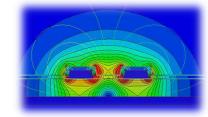

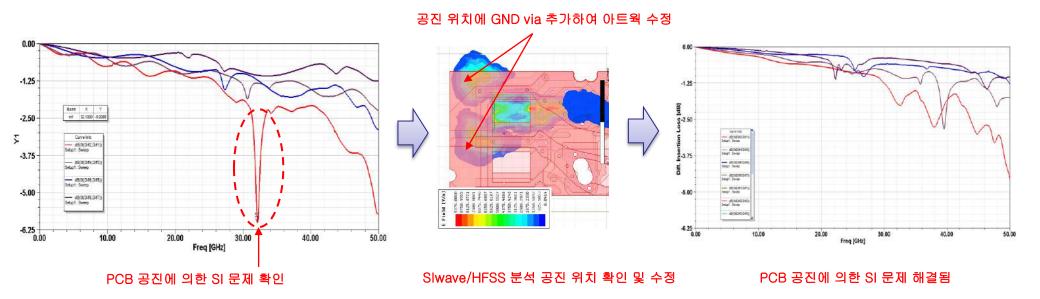

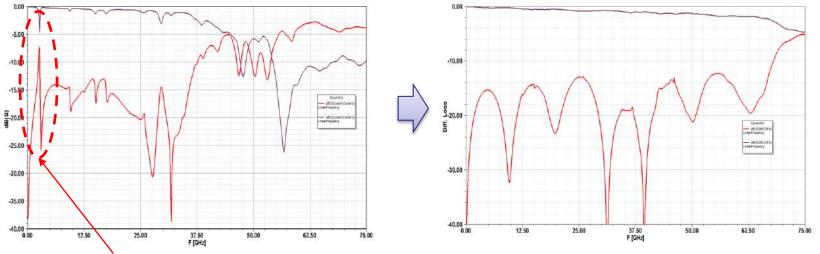

### 3-5. PCB 공진 제거:

- PCB EM SI/PI : Slwave/HFSS 이용 PCB Ground 의 공진 확인 및 GND via 추가하여 공진 제거

## ■ 3. 분석 및 설계 최적화 방법 :

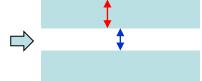

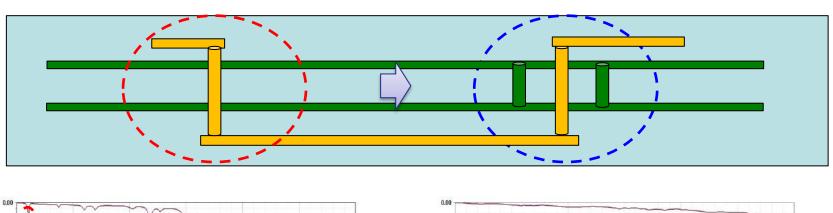

### 3-6. PCB signal return path 문제 해결:

PCB signal return path 문제 확인

- PCB EM SI/PI : SIwave 이용 PCB signal 주변 및 층간 연결 via 에 의한 return path 문제 확인하여 cross-talk 및 SI 문제 해결

### ■ 3. 분석 및 설계 최적화 방법 :

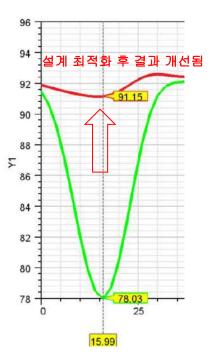

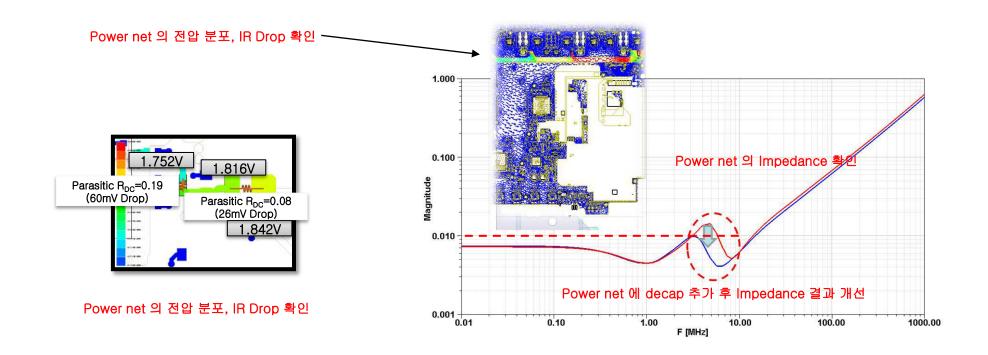

#### 3-7. PCB Power Ground PI 분석 및 최적화:

- PCB EM SI/PI: Slwave 이용 Power Net 의 IR Drop (전압 분포), 전류 분포 및 Impedance 분석 후 결과 개선 필요.

- Powe Net 의 Impedance 개선으로 Power noise 에 의한 문제 개선함.

## ■ 4. Huwin 소개 : 주요 분야

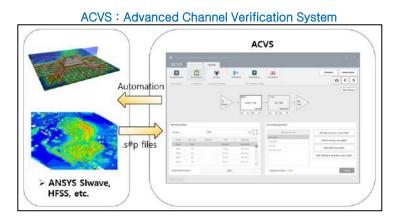

#### 초고속 SI 채널 자동분석 솔루션 (ACVS) 개발 공급

#### ANSYS Electronics, EMCoS Simulation 툴 공급

#### SI/PI 컨설팅, Training

#### 고속 채널 SI/PI 측정 및 컨설팅